聊聊英特尔与AMD各自不同的CPU整合思路及性能对比

2017 年,AMD 推出代号为“生存”的第一代 Epyc 处理器后不久。

不幸的是,这个回旋镖现在狠狠地打在了英特尔的脸上。因为仅仅几年后,这家x86公司就开始寻求自己的一套芯片集成解决方案。

从今年开始,英特尔至强6处理器开始分阶段推出,这意味着英特尔第三代多芯片至强以及首款采用AMD独特异构芯片架构的数据中心处理器也踏上了自己的征程。一条被嘲笑的技术路线。

尽管英特尔最终不得不在AMD的芯片战略面前低下傲人的头,但其采取的做法却与老对手完全不同。

克服十字线限制

在深入讨论这个话题之前,我们先来谈谈为什么新一代CPU设计放弃了传统的单片架构。这主要是受两大因素影响:口罩限产和产能。

一般来说,在制程技术没有重大改进的情况下,更多的核心必须对应更多的芯片。然而,芯片的物理尺寸面临着一个客观限制——我们称之为掩模限制,大约是800平方毫米。一旦达到这个极限,继续扩大计算能力的唯一方法就是引入更多的芯片。

我们现在看到很多产品(不仅仅是 CPU)都采用这种方法,将两个大芯片塞进同一个封装中。 Gaudi 3、的甚至Intel的Xeon都是这种技术路线的典型代表。

多芯片设计的问题在于芯片之间的桥接机制常常会造成传输带宽瓶颈,并且可能会引入额外的延迟。虽然情况不像将工作负载分散到多个插槽那么严重,但实际影响相当大,因此一些芯片设计者更愿意使用较少数量的大型芯片来实现计算能力扩展。

然而,这种较大芯片的制造成本也非常昂贵,因为芯片尺寸越大,缺陷率越高。于是,使用更多但更小的芯片成为了一个有吸引力的方向。这也解释了为什么AMD在设计中使用如此多的核心——在最新的Epyc型号中,芯片数量已经高达17个。

讲完了上述背景知识,接下来我们将深入探讨Intel和AMD分别在其最新的Xeon和Epyc处理器中采用的不同设计理念。

AMD的老套路

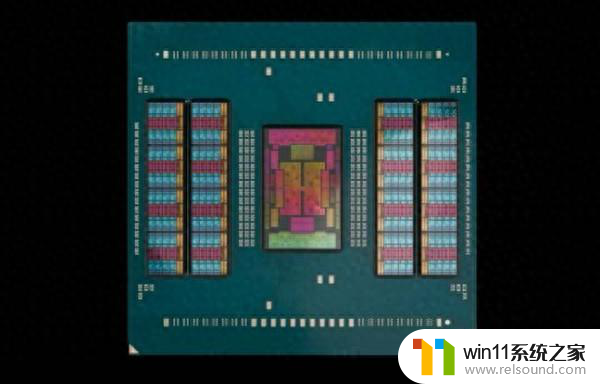

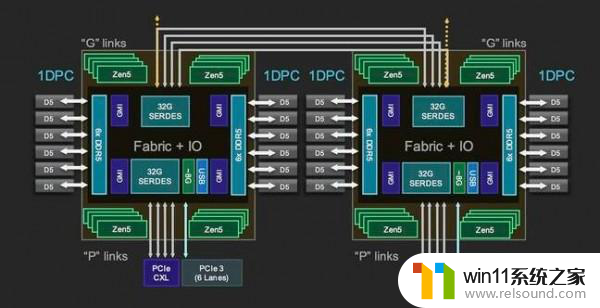

让我们从AMD第五代Epyc Turin处理器开始。具体来说,我们重点关注128核Zen 5版本的芯片,该芯片拥有16颗4纳米核心复合芯片(CCD),辅以基于台积电6纳米工艺技术的单I/O芯片(IOD)。

AMD最新一代Epyc配备多达16个计算芯片

很多朋友可能觉得这个数字听起来很耳熟。这是因为AMD在其第二代Epyc处理器上采用了基本相同的设计方案。相比之下,第一代 Epyc 没有单独的 I/O 芯片。

正如已经提到的,使用大量较小的计算芯片意味着 AMD 可以实现更高的产量,同时还能确保 Ryzen 和 Epyc 处理器之间的芯片共享。

如果这些核心看起来很熟悉,那是因为 AMD 的 Epyc 和 Ryzen 处理器实际上使用相同的计算芯片。

此外,当使用8核或16核CCD且每个CCD对应32MB L3缓存时,AMD还可以根据缓存和内存按比例扩展核心数量,具有更大的灵活性。

例如,如果我们需要一个 16 核 Epyc(根据软件许可条款,这是高性能计算工作负载最常见的 SKU 配置),那么实现我们目标的更好方法是使用两个八核核心。核心CCD,两者共享64MB L3缓存。当然,我们也可以使用16个CCD,每个CCD对应一个活动核心,并内置512 MB缓存。虽然听起来很疯狂,但这两种设计选项实际上都存在。

AMD 第五代 Epyc 处理器遵循传统模型,在单个中央 I/O 芯片周围排列 16 个计算核心。

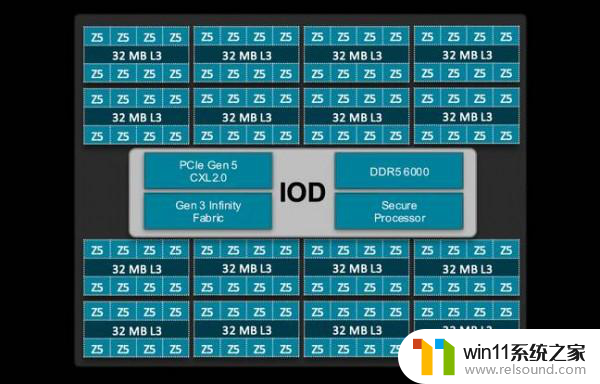

另一方面,I/O芯片负责除计算之外的几乎所有管理任务。包括内存、安全、PCIe、CXL和其他I/O(如SATA),同时还承载芯片CCD和芯片之间的通信。其他插槽。骨干通信。

AMD Epyc Turin I/O 芯片详细图

将内存控制器放置在 I/O 芯片之上既有优点也有缺点。从好的方面来说,这意味着在大多数情况下,内存带宽可以独立于核心数量进行扩展。缺点是某些工作负载的内存和缓存访问延迟可能更高。我之所以在这里强调“也许更高”,是因为具体情况往往取决于具体的工作量。

至强的核心粒子探索之旅

话题来到了英特尔。这家芯片制造商对多芯片处理器的设计方法与AMD有很大不同。尽管现代至强处理器也采用计算和I/O芯片相互独立的异构架构,但它们只出现在特定型号上。

英特尔首款多芯片Xeon处理器,代号为,采用单个中核芯片或四个极高核芯片。每个芯片都有自己的内存控制器和内置I/O功能。 。虽然采用了类似的设计模式,但核心数更高的 SKU 上使用了两颗更大的芯片。

正如您所看到的,在 和 之间,英特尔将四个中型芯片替换为两对以几乎网状图案排列的较大芯片。

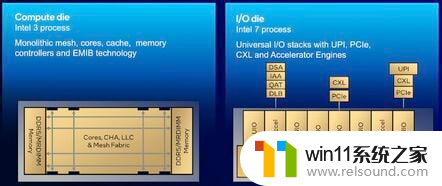

这一切都随着Xeon 6的发布而改变。这次Intel将I/O、UPI链路甚至加速器都搬到了两颗基于Intel 7处理技术的芯片上,而集中部署的是一到三颗使用Intel 7处理器的计算芯片。 Intel 3 处理技术。

出于稍后我们将详细讨论的原因,我们先把重点放在Intel寄予厚望的Xeon 6处理器上,多核暂时放在一边。

看看Intel的计算芯片,我们会发现它与AMD的主要区别之一就是每个计算模块至少内置43个核心,可以根据SKU来开启和关闭。换句话说,要实现同样的128个核心,Intel需要的芯片数量比AMD少得多;但由于前者的单芯片尺寸较大,因此制造良率必然会相应降低。

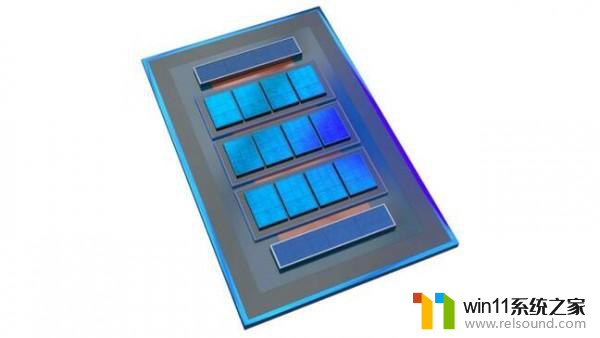

根据 SKU 配置的不同,两个 I/O 芯片之间将放置一到三个计算芯片。

除了更多的内核之外,英特尔还选择将这些芯片的内存控制器放置在计算芯片本身的顶部,支持每个芯片四个通道。这种设计理论上应该可以减少访问延迟,但这也意味着如果想要获得全部 12 个内存通道,则必须选择具有 3 个计算芯片的版本。

至于之前报道的6900P系列系统,则不必担心这个问题,因为其所有SKU都配备了三颗板载计算芯片。但也可以看出,其72核版本仅使用了封装中的一小部分芯片。我们之前讨论的高性能计算中心的 16 核 Epyc 也是如此。

另一方面,英特尔的 6700P 系列系统将于明年初推出,并计划配备一到两个计算芯片,具体取决于客户所需的内存带宽和内核数量。这意味着内存最多将被限制为8个通道,而当配备单个板载计算芯片时则只有4个通道。我们对HCC和LCC芯片上的内存配置还不太了解,不排除Intel可能在这些部件上增强了内存控制器。

与 AMD 的 Epyc 一样,英特尔的 Xeon 处理器现在也采用异构设计架构,同时包含计算和 I/O 芯片

Intel的I/O芯片设计相当轻薄,主要搭载PCIe、CXL和UPI链路的组合,用于与存储、外设和其他插槽进行通信。除此之外,我们还发现了大量用于直接流式传输(DSA)、内存分析(IAA)、加密/解密(QAT)和负载平衡的加速器。

据了解,英特尔选择将加速器放置在I/O芯片上的部分原因是为了将其放置得更靠近数据,以确保数据能够高效地流入/流出芯片。

下一步发展将走向何方?

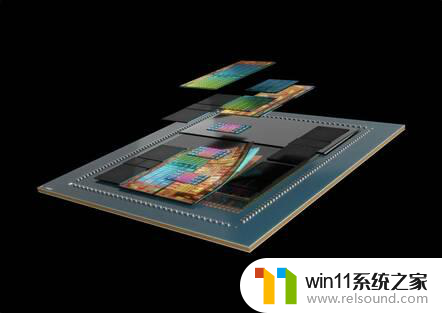

从表面上看,英特尔下一代多核处理器(代号Intel)将于明年上半年推出。它具有相似的外观,具有两个I/O芯片和三个计算模块。

整个产品看起来像是一个缩小版,但这显然只反映了芯片结构,下面还隐藏着更多的核心。

然而,眼见有时并不一定是真的。据我们所知,这三颗计算芯片实际上只是芯片结构,其下方隐藏着更多更小的计算芯片。这些核心布置在有源芯片中介层上。

从英特尔今年早些时候发布的显示渲染图来看,每个封装最多可容纳12个计算芯片。芯片中介层的使用也并不新鲜,它可以带来很多好处,包括比传统基板更高的芯片间带宽和更低的延迟。有的朋友可能注意到了,这样的设计与Intel之前最高核心数的144核计算芯片有很大不同。

从英特尔今年晚些时候发布的渲染图来看,.NET 中可能还有更多隐藏核心。

当然,我们只能从渲染图中看到一丝相关技术的影子,并不意味着它会在明年真正与广大用户见面。

更大的问题可能是 AMD 接下来将把其核心架构带到哪里。看看AMD的128核Turin处理器,你会发现封装内没有太多的空间可以容纳更多的芯片;只有Zen处理器家族还有一定的回旋余地。

首先,AMD 可以选择更大的封装,为额外的芯片腾出空间。或者,芯片制造商可以将更多内核封装到更多数量的芯片中。然而,我们怀疑 AMD 的第六代 Epyc 最终可能看起来与其 MI300 系列加速器更加相似。

它将 24 个 Zen 4 核心、6 个 CDNA 3 GPU 芯片和 128 GB HBM3 内存集成到同一封装中,以实现高性能计算工作负载。

大家可能还记得,曾有一款与 MI300 X GPU 一起推出的 APU,将芯片内的两个 CDNA3 模块替换为三个 CCD,对应 24 个 Zen 4 计算核心。这些计算模块堆叠在四个 I/O 芯片上,并连接到八个 HBM3 模块组。

虽然目前还只是猜测,但 AMD 未来采用类似的设计,比如用额外的 CCD 替换所有内存和 GPU 芯片,是完全合理的。这样的设计肯定会带来更高的传输带宽和更低的芯片间通信延迟。

实际答案是否正确,只能留待时间来证明。我们预计AMD第六代Epyc处理器将于2026年底正式上市。